Краткий анонс доклада включает весьма интересные факты:

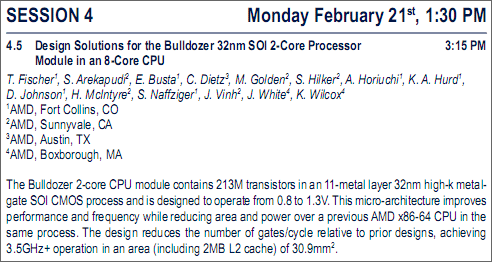

Итак, двухъядерный процессорный модуль поколения Bulldozer включает 213 миллионов 32-нм транзисторов с High-K-диэлектриком и металлическим затвором, характеризуясь рабочим напряжением в пределах 0,8-1,3 В. Новая микроархитектура обещает рост производительности, наряду с уменьшением площади кристалла и уровня потребляемой мощности. Частота топового Bulldozer поначалу будет находиться на отметке 3,5 ГГц, но при активации алгоритма автоматического разгона Turbo Core 2.0 это значение, скорее всего, достигнет 4,0 ГГц в режиме полной загрузки ЦП.

В целом 8-ядерный Bulldozer будет состоять более чем из миллиарда транзисторов, поскольку кроме четырех двухъядерных модулей (852 млн. транзисторов) требуется разместить кэш-память третьего уровня, контроллер памяти и северный мост (блок NB), а это еще примерно 250-300 млн. транзисторов.