К сожалению, слухи о двукратном увеличении числа блоков FPU у процессоров AMD Steamroller не оправдались. Как и у Bulldozer с Piledriver, у «парового катка» в одном x86-модуле будет два блока целочисленных операций и один 256-битный блок операций с плавающей запятой. На это указывает сама AMD в документе, подготовленном к конференции Hot Chips (27—29 августа 2012 г.).

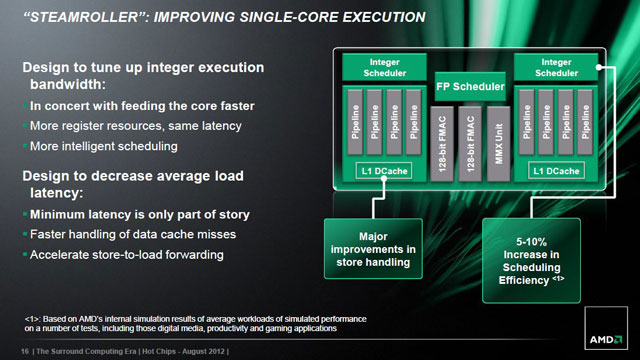

Основное внимание при доработке Piledriver (сложно назвать Steamroller совершенно новым проектом) будет уделено оптимизации загрузки ядер и уменьшению задержек при операциях с данными. В Саннивейле попробуют поднять производительность отдельных ядер, что на сегодняшний день является слабым местом ЦП поколения K11.

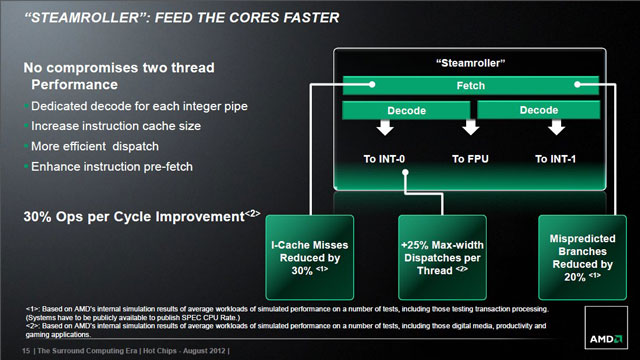

Для оптимизации загрузки ядер (потоков) в составе модуля будет увеличен кэш инструкций, предусмотрены выделенные декодеры для каждого целочисленного конвейера, улучшена передача команд (dispatch) и предсказатель ветвлений. Количество обрабатываемых операций за такт увеличится на 30%. Высокие рабочие частоты Bulldozer и Piledriver (~4 ГГц) будут как минимум сохранены.

Источник:

Legit Reviews

AMD Steamroller: революции не будет?

29.08.2012 14:23