Western Digital и Kioxia сообщили об успешной разработке нового поколения флэш-памяти 3D NAND. Микросхемы, выполненные по технологии BiCS5 (Bit-Cost-Scaling 5-го поколения), насчитывают 112 слоёв, а их коммерческий выпуск будет запущен во второй половине этого года. Первыми с конвейеров сойдут 512-гигабитные чипы 3D NAND TLC, опытное производство которых начнётся в ближайшую пару месяцев. В будущем к ним примкнут микросхемы TLC объёмом 1 Тбит и QLC вместимостью 1,33 Тбит.

Благодаря переходу с 96- на 112-слойные микросхемы 3D NAND производители рассчитывают нарастить суммарную ёмкость чипов с одной пластины на 40%, что скажется на себестоимости продукта. Вместе с этим снизятся задержки ввода-вывода, а скорость обмена информацией увеличится в полтора раза. Выпуск новых микросхем будет осуществляться на заводах Western Digital и Kioxia, расположенных в японских городах Йоккаити и Китаками.

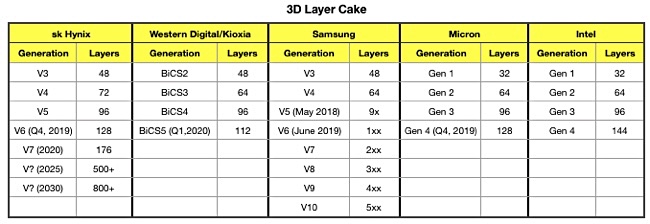

Заметим, что другие вендоры смогли опередить Western Digital и Kioxia при переходе на 100(+)-слойные чипы 3D NAND. К примеру, Samsung начала их выпуск ещё в середине прошлого года, SK Hynix и Micron представили 128-слойные микросхемы в предыдущем квартале, а Intel в этом году проложит SSD на 144-слойных чипах 3D NAND QLC, о чём было объявлено ещё в сентябре.

Источник:

Blocks and Files