Тайваньский контрактный производитель TSMC наряду с Samsung Electronics являются локомотивами современной полупроводниковой индустрии. Первая компания уже к середине этого года обещает начать выпуск кремниевых пластин по 5-нм технормам следующего поколения (N5 согласно внутренним спецификациям).

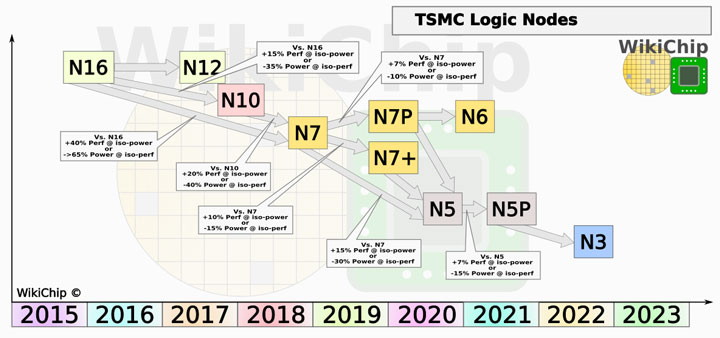

По оценкам профильного ресурса WikiChip, плотность транзисторов в N5 может вырасти в 1,84 раза по сравнению с текущими 7-нм нормами. Кроме того, это первый техпроцесс, разработанный непосредственно для экстремальной литографии EUV с количеством слоев десять и более. К примеру, N7 и N7P используют глубокую литографию DUV, а улучшенные N7+ и N6 подвергаются ограниченному воздействию EUV на нескольких слоях.

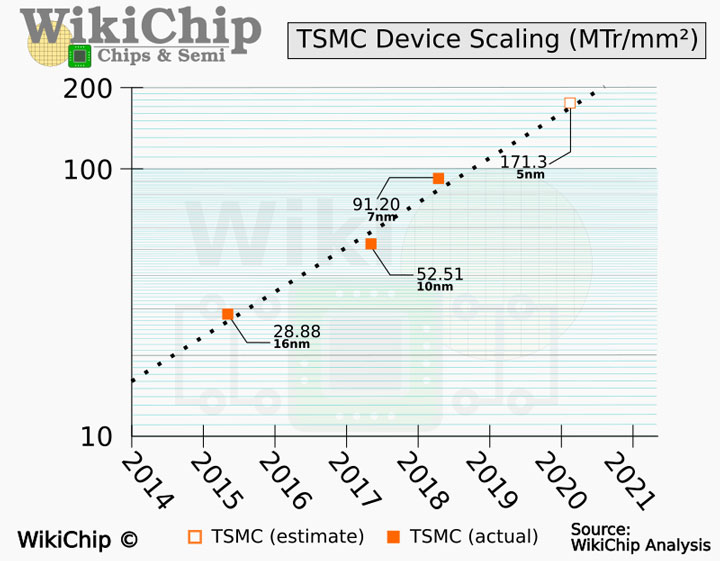

В абсолютных значениях речь идет о 171,3 миллионах транзисторов на квадратный миллиметр. Для сравнения, у 7-нм техпроцесса этот показатель составляет 92,1 МТр/мм², а у 16-нм техпроцесса всего лишь 28,88 МТр/мм². Как видим, данный график демонстрирует впечатляющий прогресс TSMC за последние пять лет. Крупнейшим клиентом TSMC на ниве N5 должна стать компания Apple с их чипами A14 Bionic.

Кроме того, TSMC N5 является по-настоящему инновационной технологией, в то время как 5-нм решение Samsung представляет собой лишь минимально оптимизированный 7-нм техпроцесс, более соответствующий N7P или N6. Тем временем Intel планирует освоить выпуск 7-нм чипов к концу 2021 года.