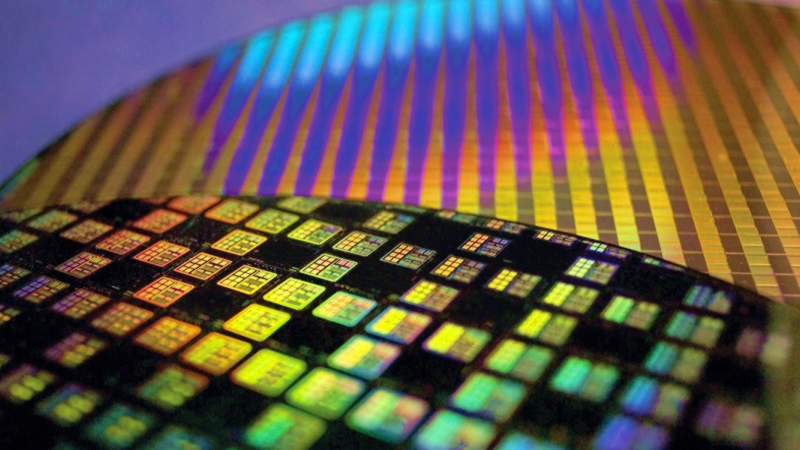

Контрактный производитель полупроводников Taiwan Semiconductor Manufacturing Company (TSMC) объявил планы по освоению новых технологических норм. В частности, уже в следующем году чипмейкер намерен приступить к опытному выпуску микросхем по 3-нм техпроцессу, а спустя год запустить массовое производство.

Перед тем, как приступать к выпуску 3-нанометровых чипов, TSMC запустит производство по улучшенным 5-нм нормам (N5P), которые позволят на 5% увеличить рабочие частоты или на 10% снизить энергопотребление интегральных микросхем. К слову, снижение уровня дефектов в 5-нм технологии первого поколения происходит быстрее, чем в случае 7-нм узла, что является отличной новостью для клиентов TSMC.

Помимо N5P тайванцы предложат 4-нм технологию N4. Она представляет собой дальнейшую эволюцию техпроцесса N5, использующую дополнительные слои EUV, при этом адаптация микросхем под новый узел не должна занять много времени. TSMC планирует запустить 4-нм конвейер в последнем квартале 2021-го, а серийное производство будет развёрнуто в 2022 году.

Наконец, во второй половине 2022-го будет запущен массовый выпуск 3-нм микросхем. Если сравнивать с 7-нм узлом, то новая технология обеспечит 3,06-кратное увеличение плотности транзисторов, снижение энергопотребления на 51% с той же производительностью или 32,25%-ный прирост быстродействия при неизменных «аппетитах» чипов.

Источник:

Overclock3D