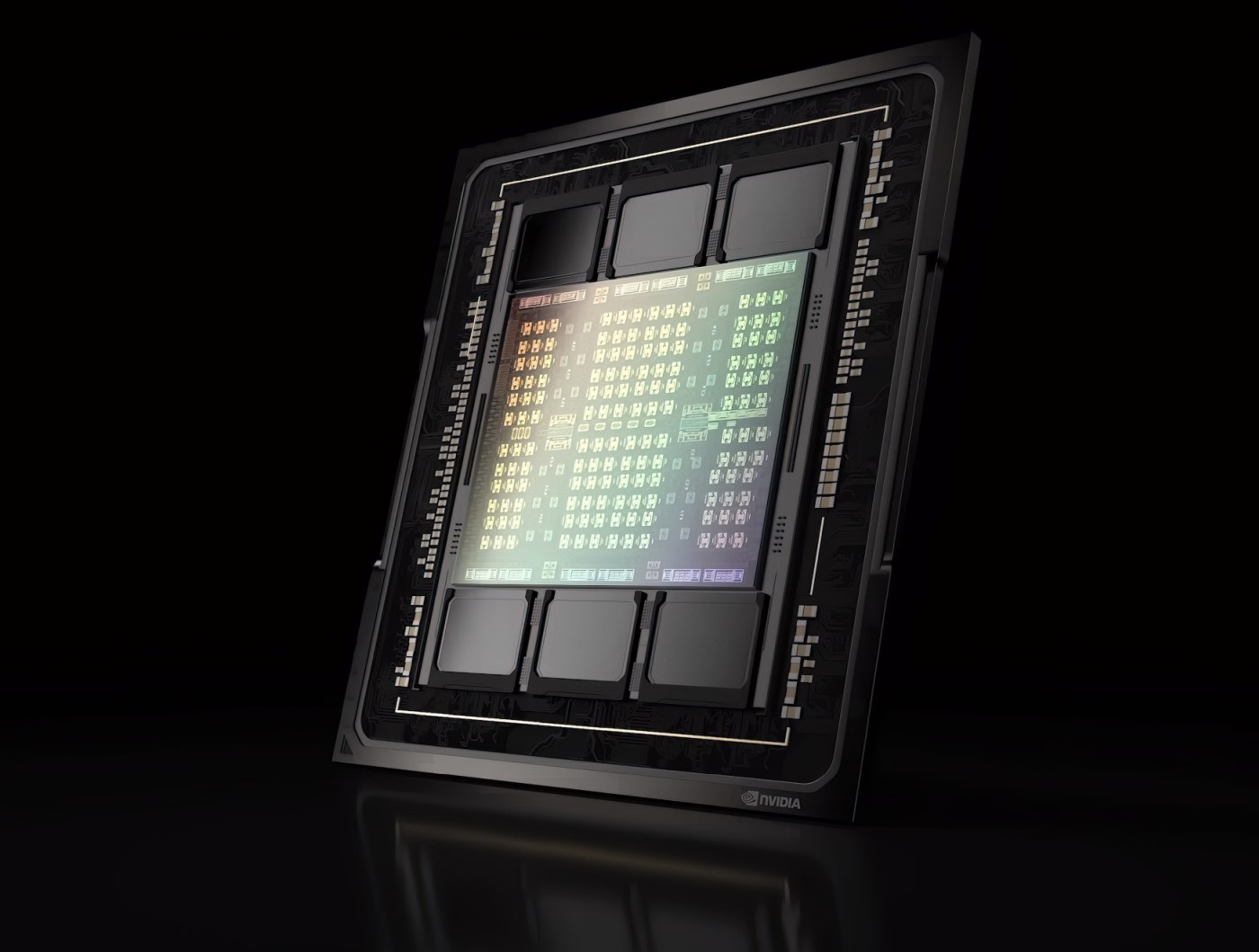

Тайванський виробник напівпровідників має намір значно наростити виробництво чипів з технологією пакування CoWoS (Chip-on-Wafer-on-Substrate). Цей метод дозволяє розміщувати на одній підкладці різні кристали для складних високопродуктивних чипів. Бурхливий зріст сфери ШІ призвів до великого попиту на такі складні чипи, і TSMC важко його задовольнити. Зокрема, за такою технологією виготовляються GPU для прискорювачів штучного інтелекту Nvidia H100 і майбутні моделі сімейства Blackwell теж будуть виконані з таким компонуванням. Причому на Nvidia припадає понад 50% всього обсягу замовлень, і зараз термін постачання прискорювачів H100 становить 10 місяців. Проблемою є не виробництво основних кристалів за тонкими техпроцесами, а брак потужностей для пакування чипів. І крім Nvidia страждають AMD та інші компанії.

TSMC має намір докласти серйозних зусиль для нарощування відповідних виробничих ліній. Компанія постійно вдосконалює виробництво та щокварталу збільшує обсяги. І до кінця року планується подвоїти загальну кількість чипів CoWoS. Але навіть у такій ситуації це не задовольнить попит, тому компанія продовжить й далі розширювати виробництво CoWoS.

Це цілком виправдано, враховуючи великі обсяги постачання Nvidia H100, а запуск нового покоління Nvidia Blackwell може підігріти апетити компаній, які розгортають серверну інфраструктуру для ШІ. Днями стало відомо, що Meta має намір придбати 350 тисяч прискорювачів Nvidia H100, і це не єдиний замовник. Загальні плани Nvidia включають постачання до двох мільйонів прискорювачів цього року. Тому TSMC прогнозує, що попит на чипи CoWoS зростатиме ще протягом 10 років.